Step By Step Guide: Interrupts with CP1L PLC

Introduction

This step-by-step guide outlines the procedure to set-up interrupt functionality on a CP1L PLC. An interrupt, when triggered, pauses the execution of the cyclic program and immediately executes a specified subprogram. Once the subprogram has been completed the cyclic program will resume from it's paused position. Each of the four possible interrupt types is explained, please refer to the CP1L CPU Unit Operation Manual Section 6, for information on which inputs can be used for interrupts on your CP1L type.

Further Reading

CP1L CPU Unit Operation Manual

Procedure

Types of Interrupts

There are multiple interrupt types available on the CP1L.

- Input Interrupts (Direct): Executes an interrupt task on an up-differentiated or down-differentiated input signal.

- Input Interrupts (Counter): Counts up-differentiated or down-differentiated input signals and executes an interrupt task when the counter reaches the set value.

- Quick-response Interrupts: Similar to Input Interrupts but reads input pulses with an ON time shorter than the cycle time (as short as 50 μs).

- Scheduled interrupts: Executes an interrupt task at a fixed time interval measured by the CPU Unit's built-in timer.

- High-speed Counter Interrupts: Executes the specified interrupt task when the CP1L's built-in high-speed counter PV matches a pre-registered value

Make sure to cycle power after making setting changes in the PLC settings to take effect.

Interrupt Priority

If interrupt Task A is being executed when interrupt Task B is triggered, Task A will continue processing without interruption. When Task A is completed, Task B will execute.

If two different types of interrupt trigger simultaneously, they are executed in the following order:

- Input interrupts (Direct or Counter mode)

- High-speed counter interrupts

- Scheduled interrupts

Duplicate Processing

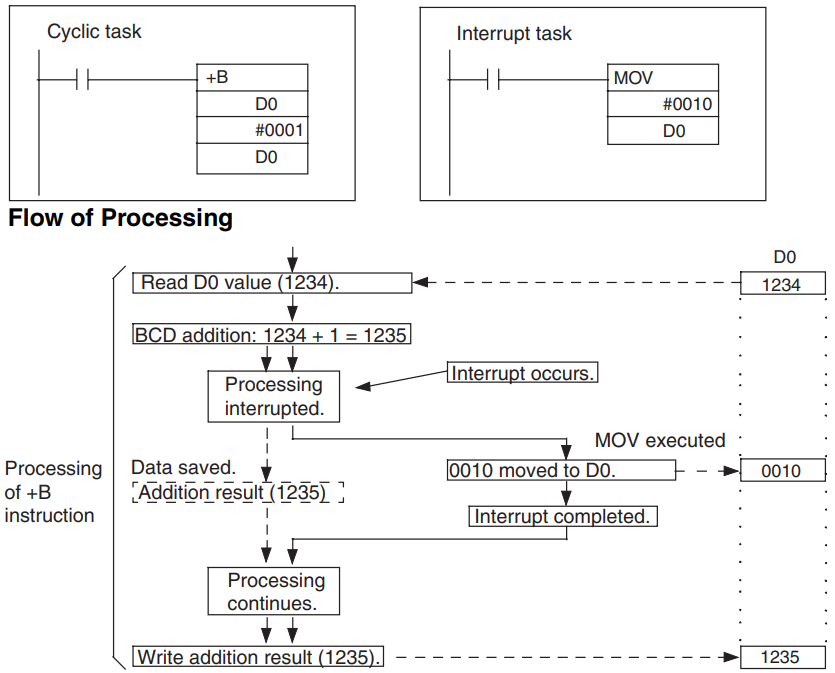

If a specific memory address is used in both a cyclic task and an interrupt task, an interrupt mask must be set to disable interrupts. This is because when an interrupt occurs, execution of the cyclic task will be interrupted immediately, even during execution of a cyclic task's instruction, and the partially processed data is saved. After the interrupt task is completed, processing returns to the cyclic task and the interrupted processing restarts with the data saved before the interrupt processing. The following example shows the effects of duplicate processing.

The interrupt occurs during processing of the +B instruction and the result is saved temporarily without being written to the destination word (D0). The interrupt task transfers the value of #0010 to D0, but the saved result of the +B instruction (1235) is written to D0 when processing returns to the cyclic task. in the end, the interrupt task's processing has no effect.

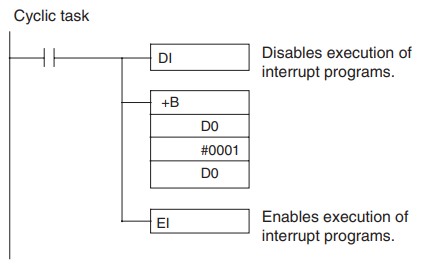

Placing the +B instruction within DI(693)/EI(694) instructions disables the interrupt programs while the instruction is being executed:

Input Interrupts (Direct)

Setting Input Functions

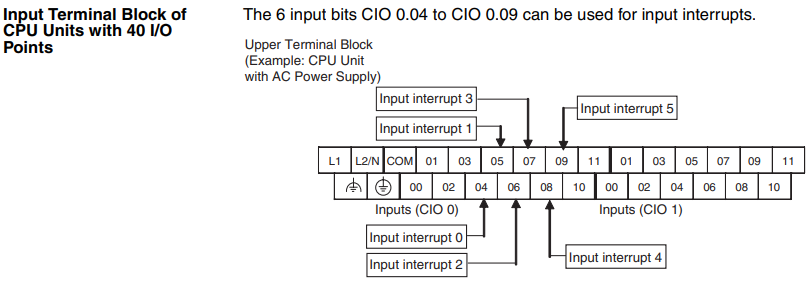

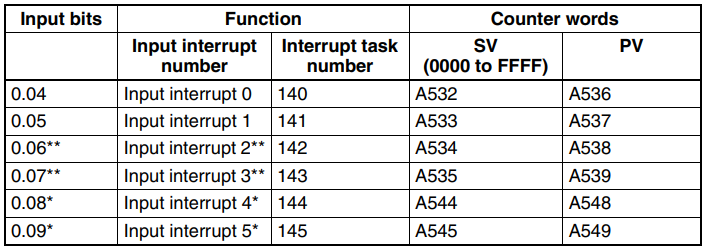

Input interrupts can be set from CIO 0.04 up to CIO 0.09 depending on the IO size of the CP1L PLC. This example uses a CP1L-M40DR-A which has 5 available interrupts:

Refer to Section 6-1 of the CP1L Operation Manual for details on the number of available interrupts for your PLC.

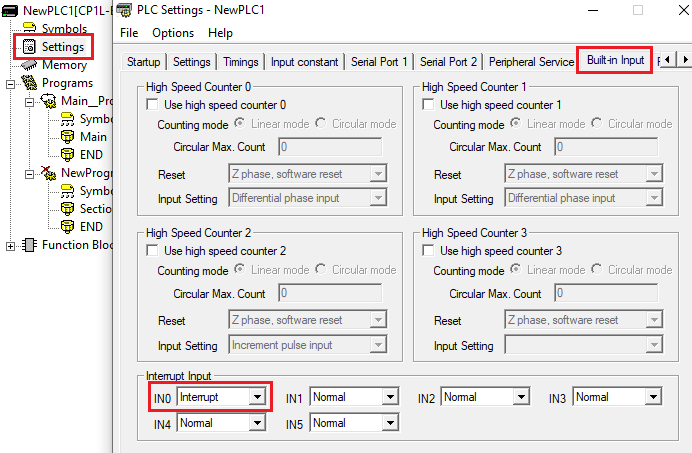

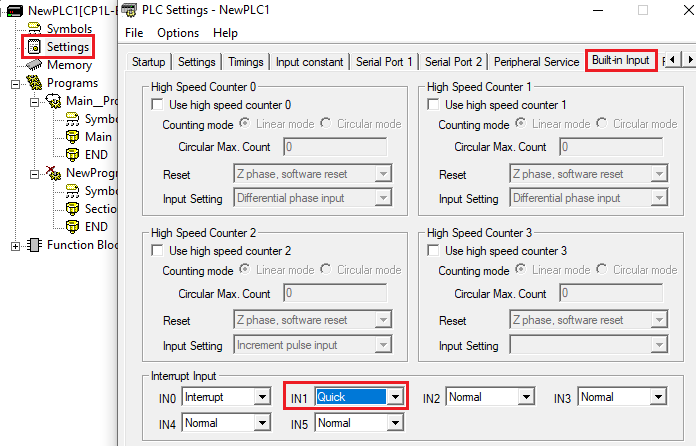

On CX-Programmer navigate to Settings > Built-in Input to set the desired interrupts. Interrupt IN0 (CIO 0.04) will be set to Interrupt for a standard up/down-differentiated interrupt.

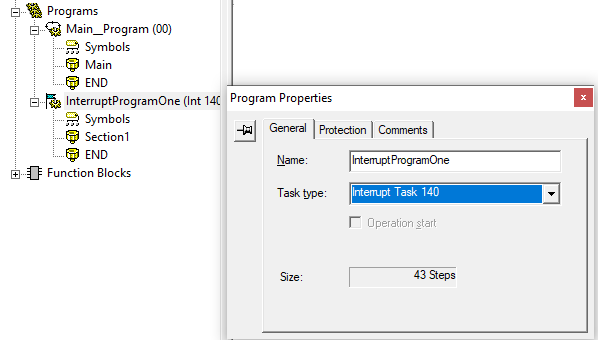

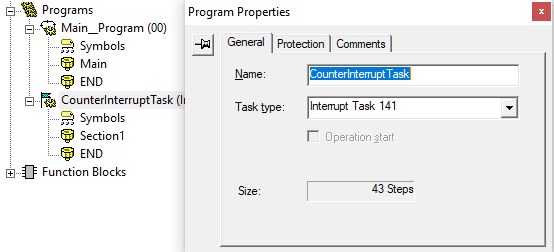

Right-click Programs > Insert Program > Ladder and select Interrupt Task 140 in the Task type option. This will create a new interrupt program linked to IN0. The code within this program will execute when interrupt IN0 (CIO 0.04) is triggered.

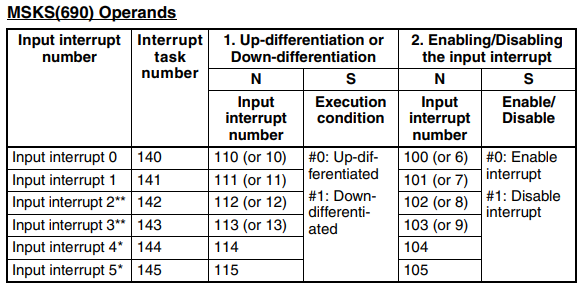

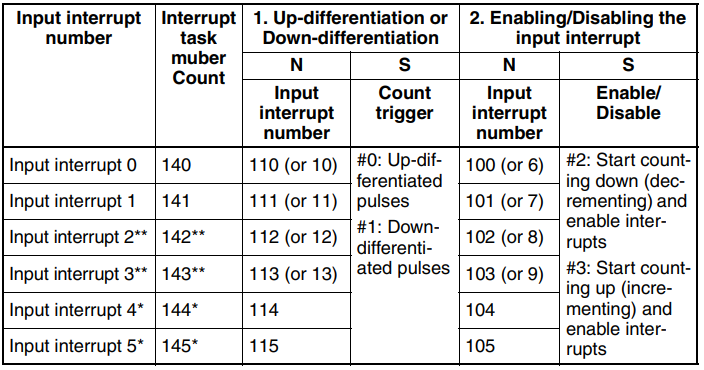

In the cyclic program, two MSKS(690) instructions must be executed in combination in order to enable the interrupt. The operands available for the MSKS(690) instruction are shown below

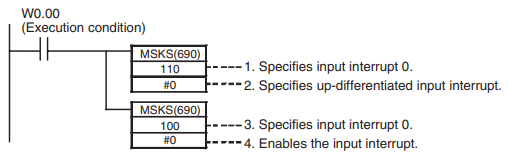

The following example shows a ladder diagram using MSKS(690) which is placed in the cyclic program.

When execution condition W0.00 goes ON, the MSKS(690) instruction will enable CIO 0.04 as an up-differentiated input interrupt. The MSKS(690) instruction only needs to be executed once, it does not need to be held on.

After the MSKS(690) instruction is executed, when CIO 0.04 goes from OFF to ON, processing of the cyclic task that is currently being executed will be interrupted and processing of interrupt task 140 will start. When the interrupt task processing is completed, processing of the interrupted ladder program will resume.

Delete

Input Interrupt (Counter)

Setting Input Functions

The physical inputs for Counter input interrupts are the same as the inputs for Direct interrupts shown in the previous example. For this example, set IN1 (CIO 0.05) to Quick as shown below. The Interrupt option allows pulses up to 5kHz, however the Quick option allows pulses up to 20kHz.

As before, create a new program and set the Task Type to Interrupt Task 141:

As with Direct Mode interrupts, the Counter interrupts use the MSKS(690) instruction for initial settings and enabling. The SV (Set Value) and PV (Present value) for the interrupt to count up too is set in Auxiliary memory as shown below:

Similar to the Direct interrupts, the MSKS(690) operands for Counter interrupts are as follows:

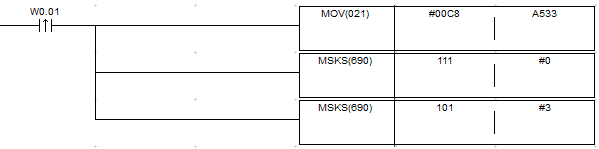

In the following ladder code, when W0.01 is turned ON, a value of 200 (0xC8 in Hex) is written to the SV (A533) for IN1. The MSKS instructions then enable IN1 as an incrementing Counter interrupt with up-differentiated pulses. Once the PV (A537) reaches the SV (A533) the interrupt task will execute and the PV will be reset to 0.

Scheduled Interrupt

The Scheduled interrupt executes an interrupt task at a fixed time interval measured by the CPU Unit's built-in timer. Interrupt task 2 is allocated to the scheduled interrupt.

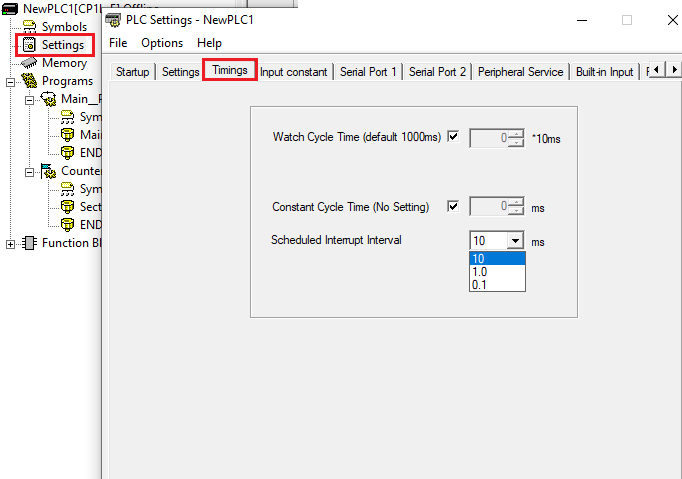

On CX-Programmer navigate to Settings > Timings to set the interrupt interval. The scheduled interrupt can be set for 10ms, 1ms or 0.1ms increments.

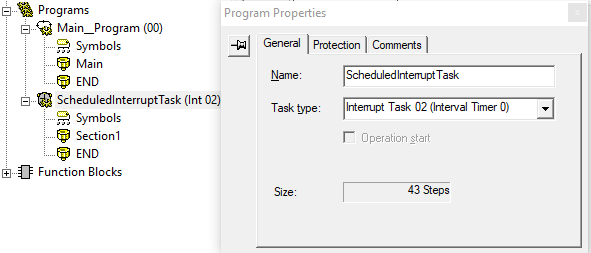

As with Direct Interrupts, create a new program and set the Task Type to Interrupt Task 02(Interval Timer 0):

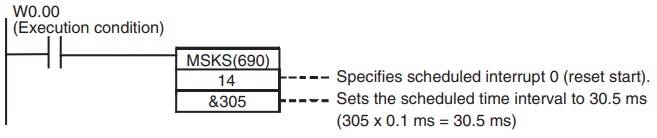

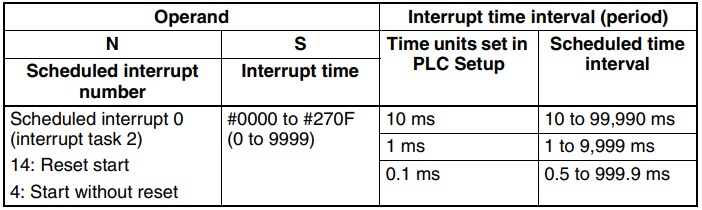

Use MSKS instructions to enable the interrupt and set the interval time. The operands are shown below:

The following ladder program enables the Scheduled interrupt and sets the interrupt interval. When W0.00 turns ON the Scheduled interrupt is enables with a Reset start and the interrupt interval is set to 30.5ms. Every 30.5ms the cyclic program will pause, and the interrupt task 02 will be executed. Note, the 30.5ms includes the time taken to execute the interrupt task, therefore it is important to ensure that the interrupt task can be executed within the interrupt interval.